## (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2003/0107565 A1 Libsch et al.

(43) Pub. Date:

Jun. 12, 2003

### (54) ACTIVE MATRIX OLED VOLTAGE DRIVE PIXEL CIRCUIT

(75) Inventors: Frank R. Libsch, White Plains, NY (US); James L. Sanford, Hopewell Junction, NY (US)

> Correspondence Address: Paul D. Greeley, Esq. Ohlandt, Greeley, Ruggiero & Perle, L.L.P. One Landmark Square, 10th Floor Stamford, CT 06901-2682 (US)

Assignee: International Business Machines Corporation

10/300,417 (21) Appl. No.:

(22) Filed: Nov. 20, 2002

### Related U.S. Application Data

Provisional application No. 60/332,389, filed on Nov. 20, 2001.

#### **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> |  |

|------|-----------------------|--|

| (52) | U.S. Cl.              |  |

#### (57)**ABSTRACT**

There is provided a circuit for driving a current mode light modulating device. The circuit includes (a) a capacitor for storing a data voltage, (b) a field effect transistor (FET) controlled by a signal on a scan line, for coupling the data voltage from a signal line to the capacitor, and (c) a current source, controlled by the stored data voltage, for driving the device with current provided from a power line. The power line is in a plane that is geometrically parallel to a plane within which the scan line is located.

### a. SCHEMATIC DIAGRAM

Fig. 3

Fig. 4

Fig. 5A

Fig. 5B

Fig. 5C

Fig. 5D

Fig. 5E

Fig. 5F

Fig. 5G

Fig. 6

Fig. 7

1.0 E-6

5.0 E-7

0.0 E+0

10

20

Time (s)

Thousands

Fig. 8B

Fig. 9B

Fig. 10A

Fig. 10B

Fig. 11

# ACTIVE MATRIX OLED VOLTAGE DRIVE PIXEL CIRCUIT

## CROSS REFERENCE TO RELATED APPLICATIONS

[0001] The present application is claiming priority of U.S. Provisional Patent Application Serial No. 60/332,389, filed on Nov. 20, 2001.

### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

[0003] The present invention relates to a pixel circuit, and more particularly, to an active matrix organic light emitting diode (AMOLED) pixel circuit that can be implemented with amorphous silicon thin film transistors.

[0004] 2. Description of the Prior Art

[0005] Several conventional active matrix drive schemes that have been used in liquid crystal display (LCDs) and are being investigated for use in AMOLEDs. These schemes include, for example, (1) an area ratio gray scale (ARG) method (M. Kimura, et al, Seiko Epson Corp., Japan, AMLDC2000), (2) a pulse width modulation method (S. Miyaguchi, et al, J. of SID, 7(3), 1999, p. 221-226), and (3) an amplitude modulation method, as used in direct view active matrix liquid crystal displays (AMLCDs).

[0006] A display-driving scheme for an array of pixels is dependent on pixel schematic, a computer aided design (CAD) layout and a manner in which control lines are brought out of the array. For example, a prior art AMOLED pixel structure having two NMOS transistors provides a current from a driver transistor that drives an OLED being switched, where the drain of the driver transistor is brought out of the array as a column line. In such a layout, the column line that supplies the current (i.e., the supply line) cannot be scanned in sync with rows lines, but must either be OFF until all the row lines are scanned or must be ON before the row lines are scanned. This aspect, as well as the layout of other control signals (e.g., whether they are brought out as row, column or common lines), dictate possible driving options. Active matrix and OLED technology, together with pixel design, dictate which driving scheme produces a least amount, or an acceptable level of, front-of-screen artifacts. For example, there is a common belief among those skilled in the display art that amorphous silicon (a-Si) thin film transistors (TFTs) are not a suitable technology for driving an OLED display, even though a-Si TFT technology is by choice and sales the mainstream technology used in AMLCDs today. Thus, conventional AMOLED displays are implemented with low temperature polysilicon (LTPS) TFT technology, and to date, no one has implemented an a-Si TFT OLED display. Some of the cited concerns are (1) an insufficient low level of drive current produced by an a-Si TFT (M. Stewart et al, IEEE IEDM, 1998, pp. 871-874; LG, SID 2001), which stems from an inherently low mobility (typically <1 cm<sup>2</sup>/V/sec and, (2) threshold voltage instabilities (J. Kanicki et al, SID 20th IDRC Proceedings, Sept. 25-28, Palm Beach, Fla., pp. 354-358).

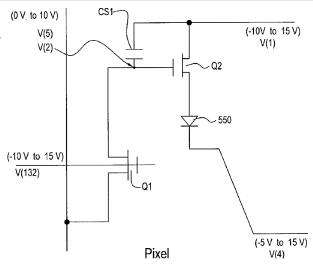

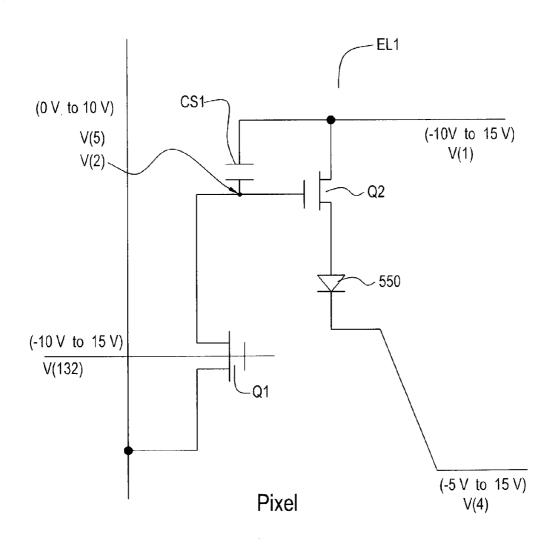

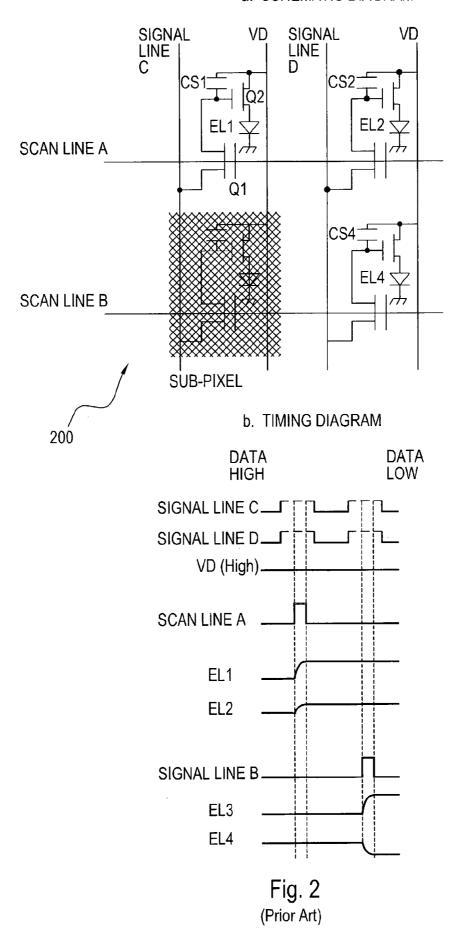

[0007] FIG. 1 is a schematic of a conventional TFT-electroluminescent active matrix pixel circuit (T. Brody et al, IEEE TED Vol. 22, No. 9, 1975, pp739-748). FIG. 2 is

a schematic and timing diagram of a conventional matrix array implementation. This same active matrix has also been applied in driving OLEDs, but one problem is that the active matrix is known to suffer from pixel-to-pixel luminance non-uniformity due to variation of a TFT threshold voltage of a driver TFT, e.g., driver Q2, (T. Sasaoka et al, 2001 SID International Symposium Digest (Sony)). Another problem is that gray-scale is related to the drain voltage of the TFT driver Q2, Vd, in a highly non-linear fashion, which makes data driver voltage corrections difficult (S. Tam et al, Proceedings of International Display Workshop 1999, AMD6-3). One of the principal purposes of the active matrix is to provide a frame-period storage in each pixel, where Q1, the pixel's data write TFT, and Cs, the pixel's data storage capacitance, store a pixel voltage as in a conventional a-si TFT LCD display. Unlike a liquid crystal display, where the LC capacitor is a voltage mode light modulator, an electroluminescent phosphor (or OLED) is a current mode light modulator and cannot be used as a voltage mode storage capacitor, thereby incorporating Cs. Cs is incorporated because a current mode light modulator cannot be used as a voltage mode storage capacitor. In addition, because of the current mode light modulator OLED element, driver Q2 provides the necessary driving current.

[0008] Several references show implementations and provide discussions of an active matrix having two TFTs per pixel (T. Sasaoka et al, 2001 SID International Symposium Digest (Sony); M. Johnson et al, 2000 International Display Workshop, pp235-238; S. Tam et al, 2000 International Display Workshop, AMD3-2, M. Kimura et al, Proceedings of International Display Workshop 1999, AMD3-1). In these references, the technology is poly-Si TFT, and the drain of all Q2 TFTs in each pixel are tied together, brought out of the active matrix as a column line, and tied to a DC voltage supply as shown in FIG. 2. The specific Q2 shown in FIG. 2 is shown in each reference listed above, i.e., each of these references include a TFT where all of the Q2 TFTs perform the same role. Because of these limitations and drawbacks, other pixels circuits have evolved, but they rely on three, four or more TFTs per pixel. See for example, (a) U.S. Pat. No. 5952789 to Roger Green Stewart and Alfred Ipri, Sep. 14, 1999, (b) U.S. Pat. No. 6229506 to Robin Dawson et al, May 8, 2001, and (c) U.S. Pat. No. 6229508 to M. Kane, May 8, 2001. However, since it is desirable to maximize fabrication yield, minimizing the number of TFTs per pixel that need to be addressed and minimizing the capacitors per pixel and the number of conductor layer crossovers, which is often proportional to the number of pixel control lines, is given serious priority. In addition the complexity of the driving scheme, and the associated costs for such items as higher performance, larger function drivers and display controllers, will increase for large number of TFTs per pixel that need to be addressed.

### SUMMARY OF THE INVENTION

[0009] The present invention provides for a pixel circuit having a minimal number of TFTs and capacitors, and a minimal number of control lines, while providing (1) a data voltage write to the pixel, and (2) a threshold voltage independent voltage-to-current conversion followed by pixel illumination.

[0010] Another feature of the present invention is to provide a driving technique for an active matrix OLED display using circuit having two TFTs per pixel.

[0011] Another feature of the present invention is to provide a pixel circuit compatible with a voltage amplitude modulated data driver and a pulse width modulated driver.

[0012] Another feature of the present invention is to provide a driving scheme that (1) minimizes an initial TFT threshold voltage shift, especially in a current drive TFT, (2) minimizes stress effects of the TFTs that results in a time dependent threshold voltage shift, especially in the current drive TFT, (3) provides reverse polarity and alternating current (AC) voltages on TFT terminals to prolong TFT lifetime, and (4) provides quick data voltage level charging of the pixel.

[0013] An additional aspect of the present invention is to provide an OLED architecture that facilitates reverse bias of a scanned OLED array. Since an OLED is a thin film device, charge can build up when driven normally in a forward bias manner. Reversing the voltage across the OLED can remove built-up charge and help to maintain low voltage operation.

[0014] Additionally, the present invention (1) maximizes pixel aperture area, (2) provides a pixel circuit and layout that can be employed for either a bottom emission AMOLED display or a top emission AMOLED display. Furthermore, the present invention maximizes manufacturing yield by providing a simple process and high yielding pixel circuitry and layout with low-cost fabrication processing.

[0015] One embodiment of the present invention is a circuit for driving a current mode light modulating device. The circuit includes (a) a capacitor for storing a data voltage, (b) a field effect transistor (FET) controlled by a signal on a scan line, for coupling the data voltage from a signal line to the capacitor, and (c) a current source, controlled by the stored data voltage, for driving the device with current provided from a power line. The power line is in a plane that is geometrically parallel to a plane within which the scan line is located.

[0016] Another embodiment of the present invention is an AMOLED display having a plurality of pixel circuits in a row. Each of the pixel circuits includes (a) a capacitor for storing a data voltage, (b) a first field effect transistor (FET) controlled by a signal on a scan line, for coupling the data voltage from a signal line to the capacitor, and (c) a second FET, controlled by the stored data voltage, for driving an AMOLED in the display with current provided from a power line. The power line is in a plane that is geometrically parallel to a plane within which the scan line is located, and the power line and the scan line are connected to each of the pixel circuits in the row.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0017] FIG. 1 is a schematic of a conventional TFT-electroluminescent active matrix pixel circuit.

[0018] FIG. 2 is a schematic and timing diagram of a conventional matrix array implementation.

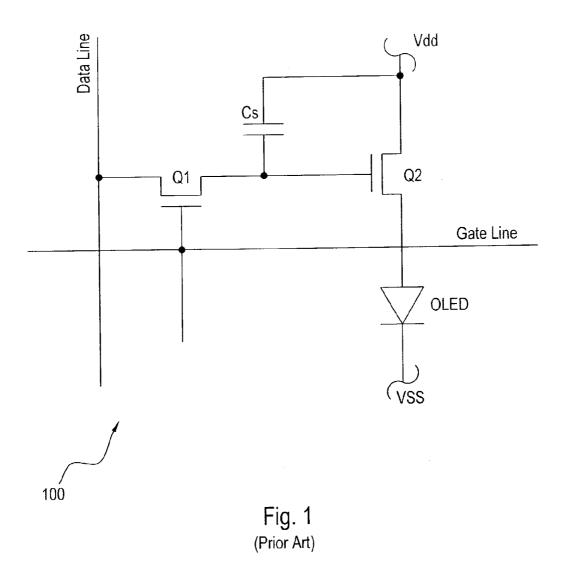

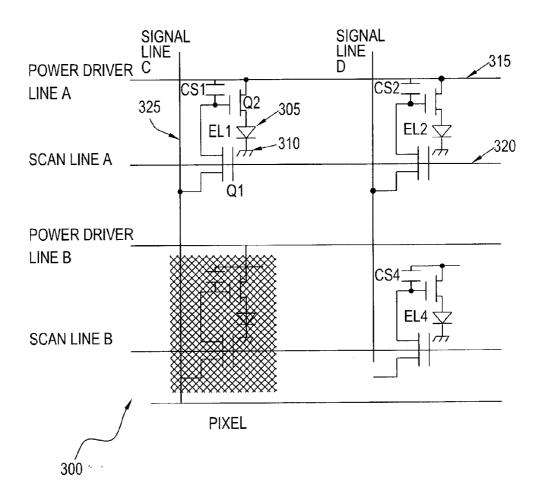

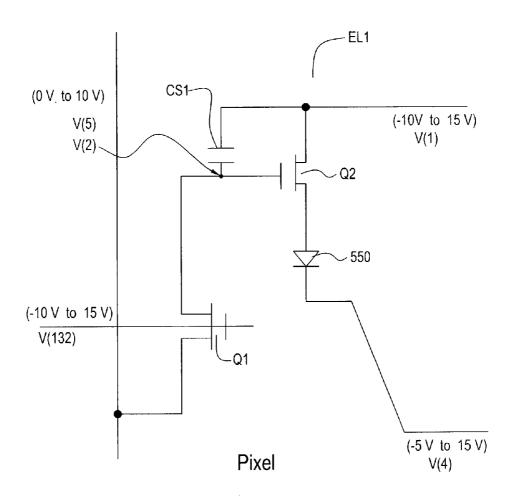

[0019] FIG. 3 is a schematic of a circuit for an active matrix in accordance with the present invention.

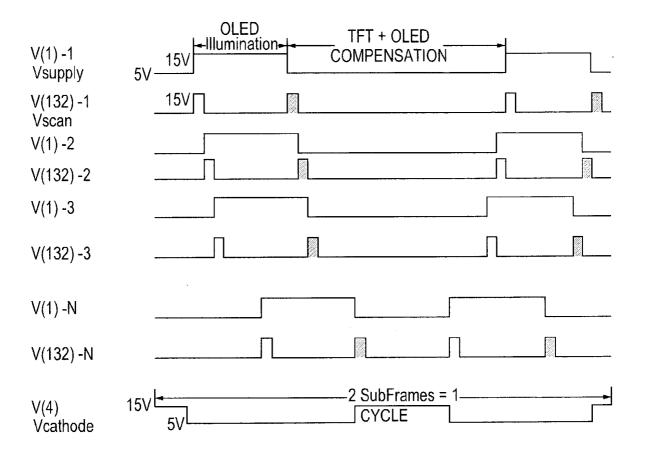

[0020] FIG. 4 is a timing diagram of a driving scheme for the circuit in FIG. 3, further extended to N rows of a display.

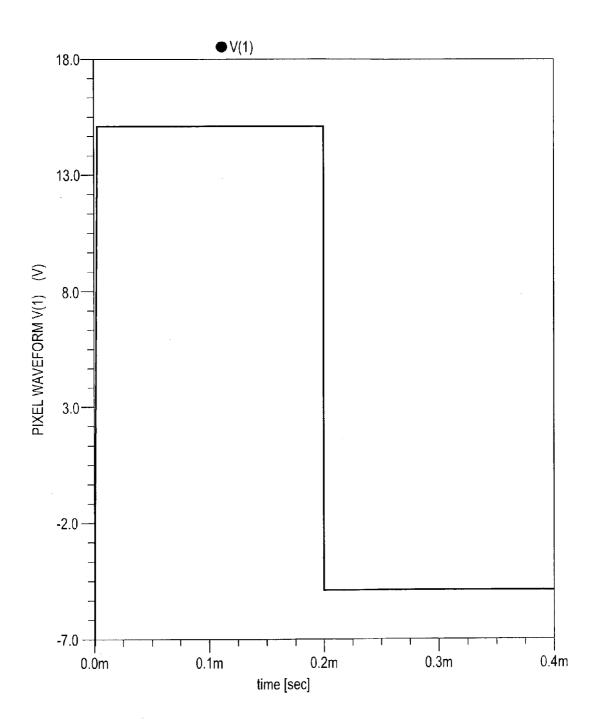

[0021] FIG. 5a is a graph of a driving scheme simulation showing waveform V(1).

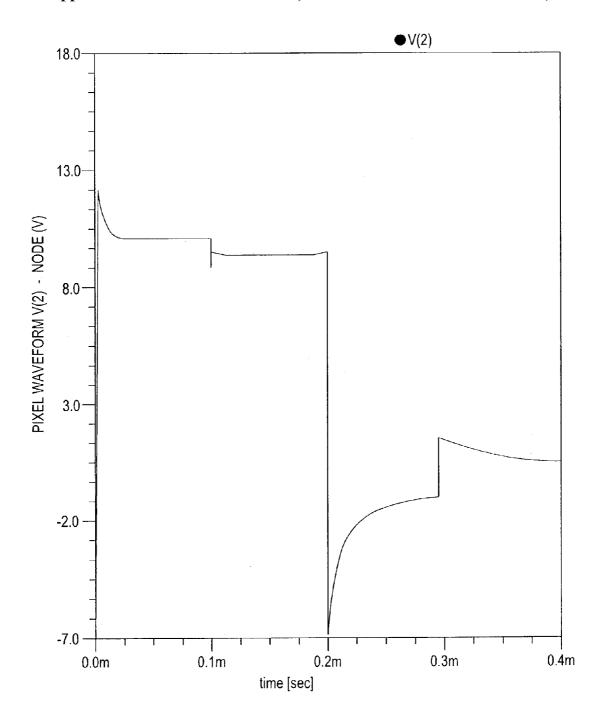

[0022] FIG. 5b is a graph of a driving scheme simulation showing waveform V(2).

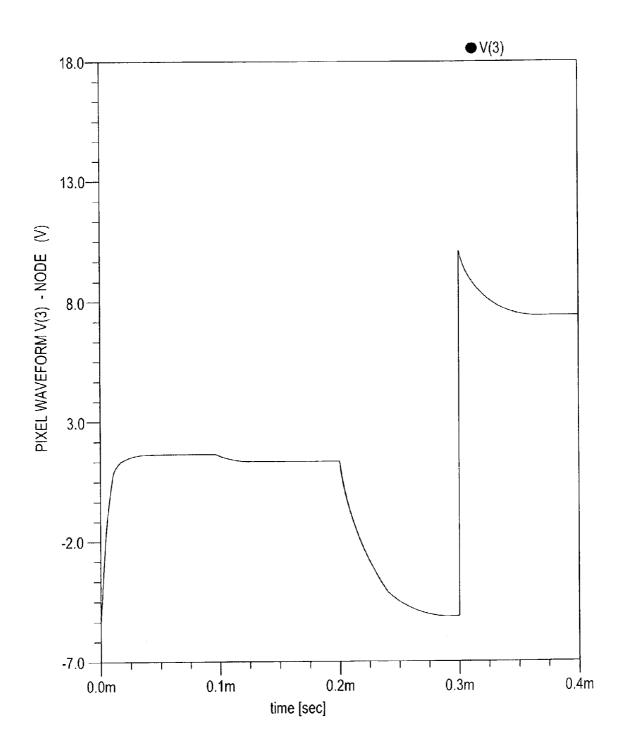

[0023] FIG. 5c is a graph of a driving scheme simulation showing waveform V(3).

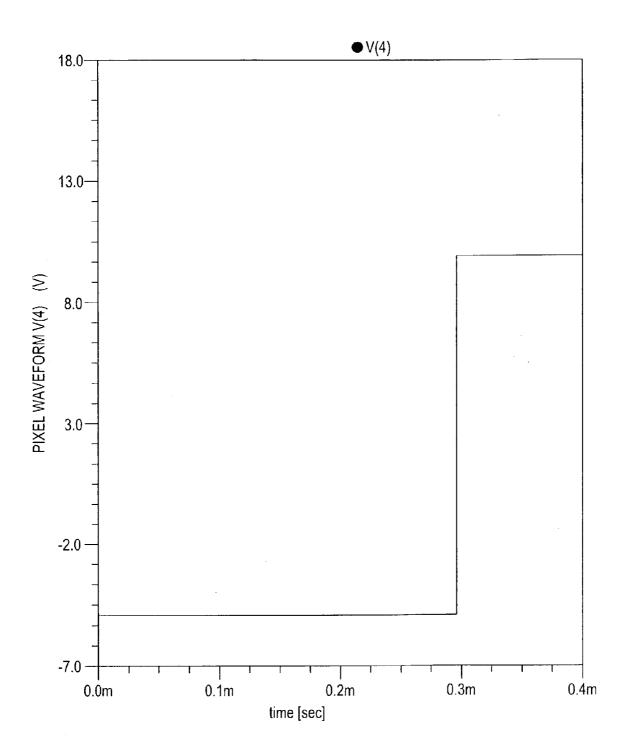

[0024] FIG. 5d is a graph of a driving scheme simulation showing waveform V(4).

[0025] FIG. 5e is a graph of a driving scheme simulation showing waveform V(5).

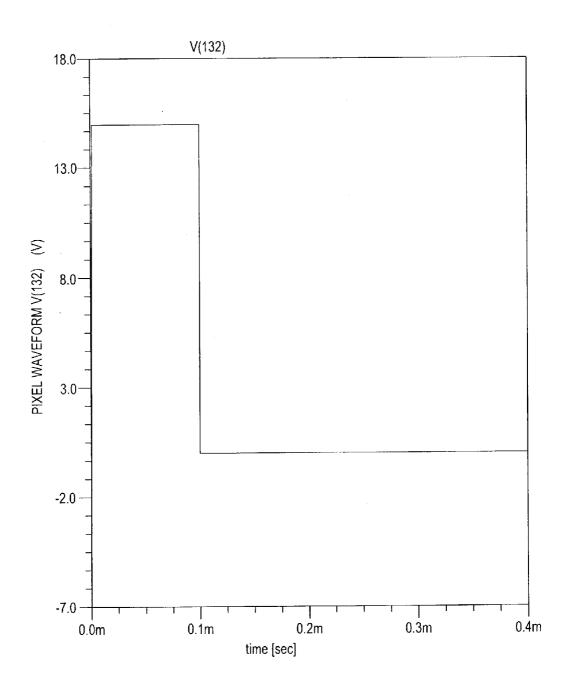

[0026] FIG. 5f is a graph of a driving scheme simulation showing waveform V(132).

[0027] FIG. 5g is a schematic of a pixel circuit being driven in accordance with the present invention.

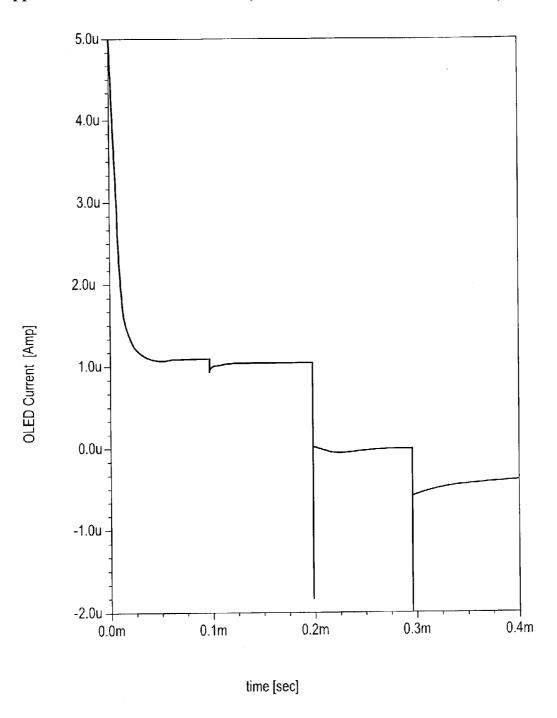

[0028] FIG. 6 is a graph of driver TFT source-to-drain current of Q2, which is equal to the OLED current, the pixel circuit of FIG. 5b.

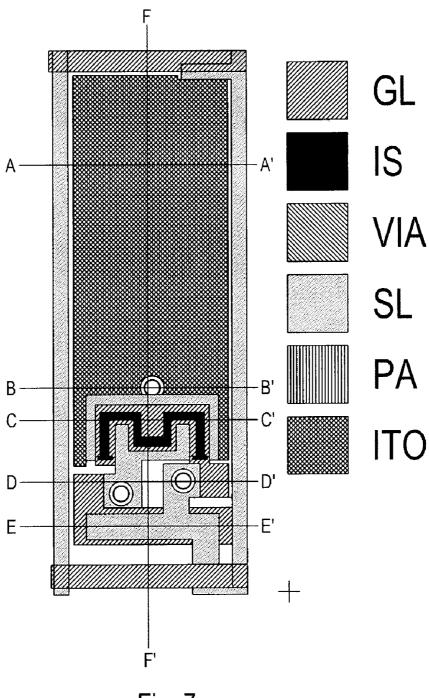

[0029] FIG. 7 is a diagram of an a-Si TFT active matrix pixel layout for the circuit of FIG. 5g, using a seven photolithographic step a-Si TFT active matrix process.

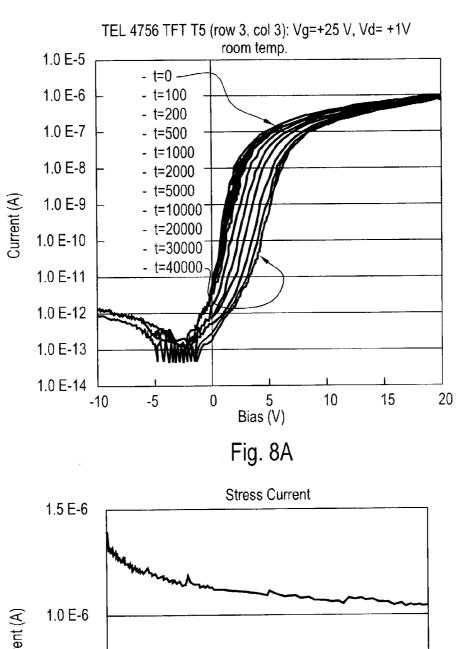

[0030] FIG. 8a is a graph of drain current versus gate bias, and FIG. 8b is a graph of stress current versus time, for TFT with channel width-to-length ratio (W/L) of 50/7, driven in linear regime (Vg=25 V, Vd=1 V).

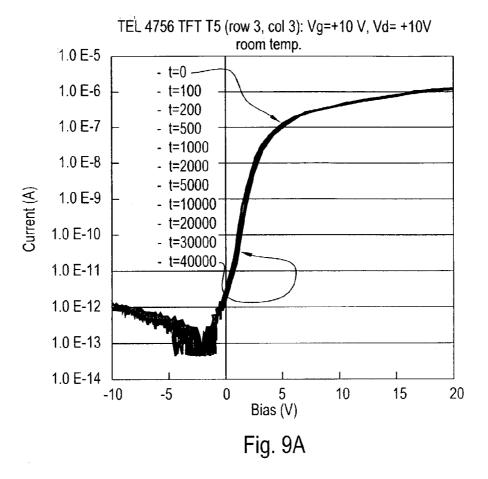

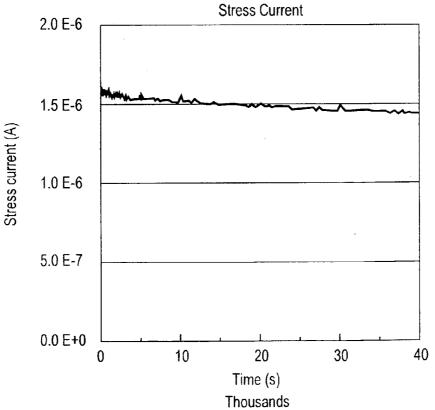

[0031] FIG. 9a is a graph of drain current versus bias, and FIG. 9b is a graph of stress current versus time, for TFT with W/L of 50/7 driven in saturation regime (Vg=Vd=10 V).

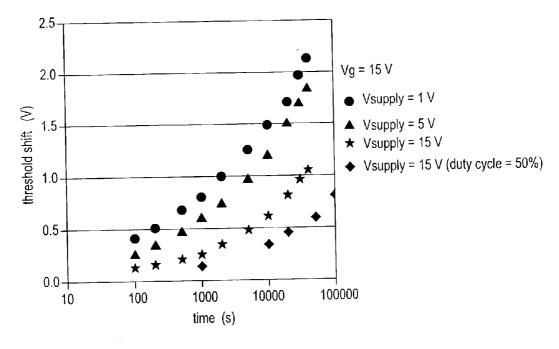

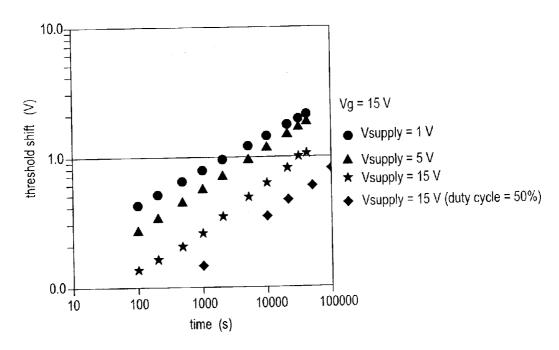

[0032] FIG. 10a is a semilog plot, and FIG. 10b is a log-log plot, of threshold shift versus stress time of TFT stability for Vg=15 V fixed.

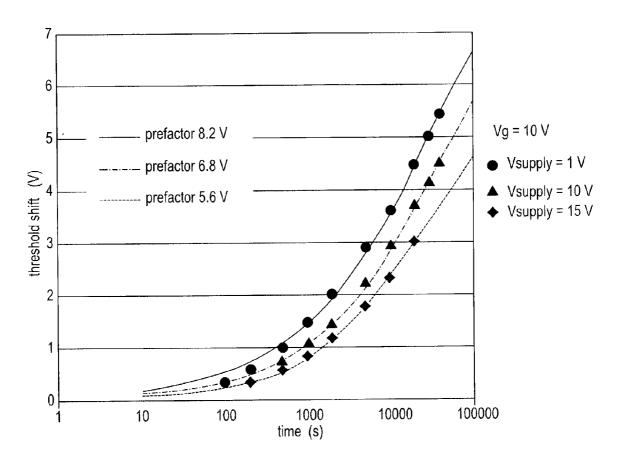

[0033] FIG. 11 is a graph of accelerated bias temperature stress at 75° C. showing the time dependence of TFT threshold voltage of an a-Si TFT with Vd as a parameter.

### DESCRIPTION OF THE INVENTION

[0034] The present invention relates to an AMOLED pixel circuit having four modes of operation, namely (1) fast data sample and hold mode, (2) sufficient drive (illumination) current mode, (3) TFT threshold voltage compensation mode, and (4) OLED compensation mode. The circuit is configured with a minimal number of components thus allowing for a favorable aperture ratio.

[0035] The pixel circuit uses a-Si technology and incorporates several features: (1) the drains of driver transistor Q2 in a row, or group of rows, are tied together; (2) the power lines are brought out of the active matrix as a row line versus the Vsupply lines that are brought out as column lines, and (3) Vdata is a pulsed signal. The present invention offers a simple implementation of a pixel circuit with only a few TFTs, and may provide a defacto pixel adaptation by a-Si TFT-OLED display makers.

[0036] FIG. 3 is a schematic of a circuit 300 for an active matrix in accordance with the present invention. Circuit 300 includes a plurality of pixel circuits, four of which are shown, namely pixel circuits EL1, EL2, EL3 and EL4. Taking EL1 as a representative pixel, it includes a storage capacitor Cs1, a data transfer transistor Q1, a driver transistor Q2, a scan line 320, a power driver line 315, a signal line 325, and a common cathode 310.

[0037] Data transfer transistor Q1 and driver transistor Q2 are connected to a common node. Storage capacitor Cs1 is connected between the common node and power driver line 315

[0038] Pixel circuit EL1 drives a current mode light modulating device, e.g., an OLED 305. Other examples of current mode light modulating devices include inorganic light emitting diodes using electroluminescent phosphor and field emission devices.

[0039] Scan line 320 is a conductor for a voltage Vscan, which is typically supplied by a row driver (not shown). Vscan is also referred to herein as V(132), and further identified by a row number (e.g., 1, 2, 3 . . . N). In an embodiment of a full display, scan line 320 is connected to a plurality of pixel circuits in a row of the display. A scan line is provided for each row of the display. That is, a first scan line for the first row, a second scan line for the second row, etc.

[0040] Power driver line 315 is a conductor for a voltage Vsupply, which is also typically supplied by a row driver (not shown). In an embodiment of a full display, power driver line 315 is connected to a plurality of pixel circuits in a row of the display. A power driver line is provided for each row of the display. That is, a first power driver line for the first row, a second power driver line for the second row, etc.

[0041] Note that Vsupply is an AC waveform, In a physical embodiment of circuit 300, power driver line 315 is preferably in a plane that is geometrically parallel to, and electrically isolated from, a plane within which scan line 320 is located. Several favorable consequences result from this configuration. For example:

[0042] (1) OLED 305 can be illuminated using a duty cycle of less than 100%;

[0043] (2) storage capacitor Cs1 can take advantage of a bootstrapping technique to accelerate charging of Cs1;

[0044] (3) waveforms on power driver line 315 and scan line 320 can be coordinated to provide threshold compensation for driver Q2; and

[0045] (4) waveforms on power driver line 315 and Vcathode 310 can be coordinated to provide reversal of trapped charges for OLED 305.

[0046] The row driver for Vscan and the row driver for Vsupply may reside on a single row driver chip or may reside on separate row driver chips. Power driver line 314 is contemplated as providing a higher current than scan line 320.

[0047] Signal line 325 is a conductor for a voltage Vdata that represents a gray level voltage amplitude. Vdata is supplied by a data driver (not shown).

[0048] Common cathode 310 is a conductor for a voltage Vcathode, which is an AC waveform. Each of pixel circuits EL1-EL4 drive an OLED, and Vcathode is common to one side of the OLED for each of EL1-EL4. In a full AMOLED array, Vcathode may be common to all of the AMOLEDs in the array, or to a subset of AMOLEDs in the array. For example, such a subset can encompass one row of pixel circuits or several rows of pixel circuits. An advantage of such a subset by row grouping is that simultaneous address-

ing of an upper portion and a lower portion of the AMOLED array provides a quicker addressing of the full array than can be accomplished by addressing single rows in sequence.

[0049] Although circuit 300 is shown with a common cathode configuration, i.e., the cathode of OLED 305 is tied to common cathode 310, it could have a common anode configuration. That is, rather than having the cathodes of the OLEDs connected together as shown in FIG. 3, the driver (e.g., Q2) in a pixel circuit could be connected to the cathode and the anodes of a plurality of OLEDs could be connected together.

[0050] Q1 operates as a pixel data write transfer switch from a gray level voltage Vdata on signal line 325 to a gate node of driver Q2 when voltage Vscan on scan line 320 is sufficiently positive. Driver transistor Q2 operates as a voltage follower to drive OLED 305. Current through OLED 305 is sourced from voltage supply Vsupply, connected to power driver line 315. As OLED 305 is driven, a threshold voltage of driver transistor Q2 changes. Voltage across OLED 305 is equal to Vsupply-Vcathode-Vgs(t), where Vcathode is a voltage on common cathode 310, and Vgs(t) is a time dependent gate-to-source voltage of Q2 Current through OLED 305 and driver transistor Q2 is proportional to (Vgs-Vt)2, where Vt is the threshold voltage of Q2. In addition, driver Q2 is biased in saturation (Vds>Vgs-Vti), where Vds is the TFT drain-to-source voltage, and Vti is the TFT initial threshold voltage before biasing induces additional TFT threshold voltage shifts. Such biasing results in a much reduced threshold voltage shift (2X to 20X) as compared to the same gate biasing of Q2 but with a smaller Vds such as in the linear region (Vds<Vgs-Vti).

[0051] FIG. 8a is a graph of drain current versus gate bias for TFT with channel width-to-length ratio (W/L) of 50/7, driven in linear regime (Vg=25 V, Vd=1 V). FIG. 8a shows driver Q2 drain to source current versus gate bias as a function of stress time for the bias-temperature-stress (BTS) condition of driver Q2 biased in the linear region with Vgs=25V, Vds=1V at room temperature. The curves from left to right result from the BTS times of 0, 100, 200, 500, 1000, 2000, 5000, 10,000, 20,000, 30,000 and 40,000 seconds, respectively.

[0052] FIG. 8b shows stress current versus stress time. Stress current in FIG. 8b is defined as the driver Q2 drain to source current for the BTS condition of FIG. 8a.

[0053] FIG. 9a is a graph of drain current versus bias for TFT with W/L of 50/7 driven in saturation regime (Vg=Vd=10 V). FIG. 9a shows driver Q2 drain to source current versus gate bias as a function of stress time for the biastemperature-stress (BTS) condition of driver Q2 biased in the saturation region with Vgs=10V, Vds=10V at room temperature. The curves from left to right result from the BTS times of 0, 100, 200, 500, 1000, 2000, 5000, 10,000, 20,000, 30,000 and 40,000 seconds, respectively.

[0054] FIG. 9b shows stress current versus stress time. Stress current in FIG. 9b is defined as the driver Q2 drain to source current for the BTS condition of FIG. 9a.

[0055] FIG. 9a (saturation region biasing) shows approximately 4 times less of a driver Q2 threshold voltage shift compared to FIG. 8a (linear region biasing), and FIG. 9b (saturation region biasing) shows approximately 2 times less

of rate of decrease in stress current compared to FIG. 8b (linear region biasing). The saturation and linear region biasing points where chosen to represent approximately equal driver Q2 drain-to-source current at BTS times equal to 0 seconds.

[0056] As a result of biasing driver Q2 in the saturation region, OLED 305 voltage and current will change much less than if driver Q2 where biased in the linear region, such as is the biasing for AMLCDs. Additional consideration must be taken into account for amorphous silicon operating voltages for the AMOLED displays of the present invention since the TFT bias is applied for a substantially larger percentage of time, i.e., duty cycles up to 100%, compared to AMLCD duty cycles of less than 1%. To further reverse any induced threshold voltage shift, a voltage of Vgs<Vti can be placed onto driver transistor Q2 as well as onto data transfer transistor Q1. Furthermore, an ability of driver transistor Q2 to faithfully reproduce a gray level current depends on a slope of a saturation region in the output characteristics of driver transistor Q2. In practice, the longer the Q2 channel, the smaller the source-drain resistance to channel resistance ratio, and hence the smaller the output source-drain current change for a given dVt, the change in threshold voltage. The voltages on the Vsupply, Vcathode, scan line and Cs1 are switched to different voltages in time to reduce or compensate for threshold voltage changes. Vcathode is the common supply applied to the common cathode electrode of 310, and scan line is the conductive line connecting the gates of Q1 on a row.

[0057] Thus, with reference to FIG. 3, the present invention thus provides a circuit, e.g., pixel circuit EL1, for driving a current mode light modulating device, e.g., OLED 305. Pixel circuit EL1 includes (a) capacitor Cs1 for storing a data voltage, data transfer transistor Q1, controlled by a signal on scan line 320, for coupling the data voltage from signal line 325 to capacitor Cs1, and (c) driver transistor Q2, controlled by the stored data voltage, for driving OLED 305 with current provided from power line 315. Power line 315 is in a plane that is geometrically parallel to a plane within which scan line 320 is located.

[0058] FIG. 4 is a timing diagram of a driving scheme for a circuit such as FIG. 3, further extended to N rows for the functions of pixel writing, OLED illumination, and TFT and OLED compensation. The driving scheme incorporates several features: (1) up to four independent modes of operation; (2) fast data sample and hold through use of bootstrapping, (3) independent row illumination, (4) row-at-a-time addressing and illumination, and (5) Driver Q2 and OLED 305 I-V characteristic shift compensation, which is noted as "OLED Compensation". The legend shows a block diagram representing an OLED array 410, and the voltage waveform inputs to OLED array 410, namely Vdata 415, Vscan 420, Vsupply 425 and Vcathode 430. In this embodiment, V(132)-1, V(132)-2, ... V(132)-N represent line waveforms analogous to Vscan 420 for row 1, 2, ... N, respectively, for OLED array 410. V(1)-1, V(1)-2, ... V(1)-N represent line waveforms analogous to Vsupply 425 for row  $\hat{1}, 2, \ldots N$ , respectively, for OLED array 410. V(4) represents the common array waveform analogous to Vcathode 430 for OLED array 410. In summary:

[0059] V(1)-1=Vsupply 425 for the first row;

[0060] V(132)-1=Vscan 420 or voltage on the gate of data transfer transistor Q1 for the first scan row;

[0061] V(1)-2=Vsupply 425 for the second row; and

[0062] V(132)-2=Vscan 420 or voltage on the gate of data transfer transistor Q1 for the second scan row,

[0063] V(1)-N=Vsupply 425 for the Nth row;

[0064] V(132)-N=Vscan 420 or voltage on the gate of data transfer transistor Q1 for the Nth scan row; and

[0065] V(4)=Vcathode 430 of voltage waveform on the common cathode.

[0066] For simplicity, voltage waveform Vdata 415 is not shown, but understood to be of valid data when Vscan 420 is high and turning Q1 on. Shown is a sequential row scan with V(132)-1 through V(132)-N being a double pulse waveform per display subframe. The first pulse defines the pixel data write operation to the gate node of driver Q2, and the second pulse writes the driver Q2 gate compensation level. Coinciding with the sequential row scan of voltage pulse V(132)-1 through V(132)-N is either the rising edge or falling edge of V(1)-1 through (1)-N, respectively. The rising edge establishes the beginning of OLED 310 illumination, where the voltage difference between V(1)-1 through V(1)-N and v(4) establish the bias across driver Q2 and OLED 310 needed for illumination of OLED 310. The falling edge establishes the end of illumination of OLED 310. Note that the row controlled V(1)-1 through V(1)-Nmakes it possible to do row-at-a-time addressing and illumination, and row independent illumination control. When the falling edge of V(1)-1 through V(1)-N coincides with the rising edge of V(132)-1 through V(132)-N, respectively, the start of driver Q2 or OLED 310 compensation is initiated. Driver Q2 compensation is through reverse biasing the gate to source and the gate to drain. Compensation benefits may result from an increase in the lifetime by threshold voltage shift decrease. Additional lifetime benefit may be derived by biasing the drain voltage lower than the source voltage, as is implemented when V(4) is high and V(1) is low. Typical voltage waveform amplitudes for a-Si TFT active matrix are shown. When V(4) is high and V(1)-1 through V(1)-N is low, the OLED 305 compensation takes place by allowing charge detrapping to take place due to the reverse biased OLED 305.

[0067] When a capacitor charges to a voltage, there can be a particle current and a displacement current. The particle current is produced by a flow of positive or negative charges onto a plate of the capacitor. Since a capacitor does not allow an instantaneous change in voltage across the capacitor, when one electrode of the capacitor sees an instantaneous change in voltage, the other electrode of the capacitor also sees the same increase or decrease in voltage. Such an instantaneous change in voltage on the plates of the capacitor, i.e., a voltage pedestal, is brought about by displacement current. Bootstrapping is a technique for introducing a sudden change in voltage on one electrode of a capacitor and inducing a displacement current to force the other electrode to follow the same voltage change.

[0068] With reference to FIGS. 3 and 4, note that OLED 305 has a terminal connected to a common electrode, i.e., common cathode 310. Vsupply is a waveform on power line 315, Vcathode is a waveform on common cathode 310, Vscan is a waveform on signal line 325, and signal line 315 has a data voltage waveform thereon. Collectively, the Vsupply, Vcathode, Vscan and data voltage waveforms

cooperate to control OLED **305**. For example, Vsupply and Vcathode cooperate to reverse bias OLED **305** to reduced trapped charge, and Vsupply, Vscan, and Vcathode cooperate with one another to reduce a threshold voltage shift of driver transistor Q2.

[0069] FIG. 5a through FIG. 5f show a driving scheme simulation, for the circuit of FIG. 5g where all node voltages are shown and defined as:

[0070] V(1)=Vsupply;

[0071] V(2)=data voltage at the gate node of driver transistor Q2;

[0072] V(3)=voltage at the anode electrode of OLED 550;

[0073] V(4)=Vcathode or the common cathode voltage;

[0074] V(5)=Vdata or the data voltage to the drain of data transfer transistor Q1;

[0075] and

[0076] V(132)=Vscan or the gate node voltage to data transfer transistor Q1.

[0077] In general, Vd or Vsupply maximum is larger than Vdata to ensure driver transistor Q2 is driven into saturation. Four independent modes of operation are shown: (1) data voltage writing to pixel during times 0 to 0.1 msec, (2) OLED illumination during times 0.1 msec and 0.2 msec, (3) Driver Q2 compensation resulting in longer driver Q2 lifetime during times 0.2 msec and 0.3 msec, and (4) OLED compensation resulting in longer OLED 550 lifetime during 0.3 msec and 0.4 msec. Typical voltage waveform amplitudes for a-Si TFT active matrix are shown. Note that when V(1) rising edge precedes V(132) rising edge at 0+seconds, the V(1) rising edge capacitively couples or bootstraps to V(2), thereby pulling up V(2). Shown is a 13V pullup on V(2). Storage capacitor Cs1 employs a displacement current through bootstrapping to facilitate storage of the data voltage. This displacement current provides quick data voltage writing onto V(2) by providing a voltage pedestal, whose voltage divider is the change in V(1) multiplied by Cs1 divided by the total capacitance on gate node driver Q2.

[0078] FIG. 6 is a graph of driver TFT source-to-drain current of Q2, which is equal to the OLED current, for the pixel circuit of FIG. 5g. FIG. 6 shows OLED 550 current versus time for the voltage node biases in FIG. 5a through FIG. 5f. It also shows current response, i.e., displacement current, at time 0 for a quick charging of a storage capacitance by boot strapping. Note the large displacement current produced from bootstrapping at time 0+ seconds.

[0079] FIG. 7 shows a layout for the pixel circuit of FIG. 5g implemented in a seven-step a-SI TFT active matrix process. There is a gate level metal (GL) or first conductor, an insulator etch stopper (IS) or the patterning of the a-Si and top insulator layer, a via (VIA) or contact hole down to the gate level, a signal level (SL) or second conductor level, a passivation and planarization insulator level patterning (PA), and an indium tin oxide (ITO) transparent conductor. The final passivation layer patterning is not shown.

[0080] FIG. 10a is a semilog plot, and FIG. 10b is a log-log plot, of threshold shift versus stress time of TFT

stability for Vg=15 V fixed. **FIGS.** 10a and 10b show the threshold voltage shift of driver Q2 versus BTS time at room temperature.

[0081] FIG. 11 is a graph of accelerated bias temperature stress at 75° C. showing the time dependence of TFT threshold voltage of an a-Si TFT with Vd as a parameter. Note that the gate drive prefactor reduction benefit exists in the TFT saturation regime even at higher temperatures.

[0082] In FIGS. 10a, 10b and 11, the parameter stepped is Vsupply of driver Q2, showing that prolonged driver Q2 lifetime is realized for larger Vsupply bias or smaller duty cycles.

[0083] This pixel circuit schematic of FIG. 3 and the driving scheme of FIG. 4 can also be applied to polysilicon (p-Si) TFT active matrix technology, however, p-Si TFT technology has other advantages/disadvantages that need to be taken into account for optimization. For example, a p-Si TFT has up to several hundred times more transconductance, typically a mobility in the range of 50 to 300 cm<sup>2</sup>NV/sec for n-channel and slightly less for p-channel, than an a-Si TFT, with typical mobility in the range of 0.1 to 2 cm<sup>2</sup>/V/sec, of similar width-to-length channel ratios. Another example is that a p-Si TFT may suffer from TFT I-V characteristic mismatching since nearest neighbor pixel TFT uniformity is more difficult to control due to an inherent recrystallization of a p-SI TFT channel region that produces area proximity random grain sizes and numbers, and non-identical grain boundary properties. The uniformity quality can be measured in a distribution of TFT threshold voltage variations, and hence a distribution of TFT drive currents. In general, P-channel p-Si TFT technology has a smaller threshold voltage distribution compared to n-channel p-Si TFT technology, as well as lower off current leakage that make it a better choice for the pixel TFTs. In general, p-Si TFT technology exhibits higher off current leakage as well as a larger threshold voltage distribution. Also, because of the higher mobility of p-Si compared to a-Si, p-Si TFTs may exhibit channel hot carrier degradation with time, a condition that is exasperated near the drain end of the gate insulator when the ratio of TFT drain voltage-to-gate voltage approaches 2. Hot carrier injection into the gate insulator causes threshold voltage shifts, where differential threshold voltage shifts between pixels are pattern-history dependent and difficult for which to compensate fully. For reasons of hot carrier injection, TFT biasing in the saturation regime (Vds>Vgs-Vth) for p-Si TFTs is less desirable, where:

[0084] Vds=drain to source voltage;

[0085] Vgs=gate to source voltage; and

[0086] Vth=threshold voltage.

[0087] In contrast, a-Si threshold voltage instabilities are typically induced by one or two of the following mechanisms; (1) charge injection from the channel interface and charge trapping in the TFT gate insulator, and/or (2) bond breaking in the a-Si semiconductor (Stabler-Wronski effect). The dominant a-Si TFT degradation mechanism is highly dependent on the a-Si and gate insulator film technology. The first degradation mechanism, charge injection and charge trapping in the TFT gate insulator, is field dependent, and hence easily controlled or limited, by the gate insulator electric field and gate insulator technology. A time, temperature and gate bias field dependence exists where TFT

threshold voltage shift, dVt, is well described by the stretched-exponential equation

$$|dvt| = |dVo|^{\alpha} \times \{1 - e^{-(t_{st}/\tau)^{\beta}}\}$$

**[0088]** where dVo=(Vgs-Vti), is approximately the initial voltage drop across the insulator,  $\tau = \tau_0 e^{(E_f/kT)}$  is the characteristic trapping time, where the thermal activation energy  $E_a = E_t \times \beta$ , with  $\beta$  being the stretched-exponential exponent.

[0089] This distribution of multiple traps in the gate insulator yields a power law time dependence  $\beta \sim 1.04$  and  $To\sim 229 K$  for the expression  $\beta=(Tst/To)-\beta o$  for positive gate voltages. Typical values are  $\beta\sim 0.248$  and 0.22,  $E_t\sim 1.17$  and 0.97 eV for positive and negative gate bias stress, respectively.

**[0090]** For the gradual channel conditions, i.e., TFT linear region, where Vds<(Vgs-Vth),  $\alpha$ -1. For the TFT operating in the saturation region,  $\alpha$  can be dramatically reduced below 1.

[0091] The design aspects of the pixel layout and the driving method of the present invention incorporate several advantages. Three of these advantages are described below.

[0092] A first advantage exists for pixels biased in the saturation region, where the larger the Vds-to-Vgs ratio, the lower the threshold voltage shift, dVt. Also, note that a positive and negative Vgs bias produces a positive and negative dVt shift, respectively, with the zero Vth shift crossover being at Vgs-Vti, where Vti is the initial threshold voltage.

[0093] A second advantage exists if negative Vgs bias can be applied to offset the positive Vgs bias induced dVt. In addition,  $\beta$  may be gate pulse frequency dependent because of a thermal release of trapped charge between gate pulses, and a typical difference in the  $\beta$  values are 0.233 for gate pulse conditions between ~0.125% and ~33.3% duty cycle, to 0.248 for steady state, i.e., duty cycle=100%, gate conditions. Since  $\beta$  is gate pulse frequency dependent,

$$dVt(t_{st}(\text{pulse})) \left[ \frac{100\%}{DC} \right] < dVt$$

[0094] where  $t_{\rm st}({\rm pulse})$  is the TFT accumulated pulse width stress time, and DC is 100% duty cycle. In addition, some insulators may favor injection of the opposite charged carriers, holes or electrons, which produces less net effectively charged gate insulators, and less dVt.

[0095] A third advantage exists in minimizing dVt. This is achieved if pulse bias, i.e., duty cycle<100%, is used rather than 100% duty cycle.

[0096] The present invention provides for a line-sequential scanning and constant-voltage driving sequence to drive a pixel composed of two TFTs, i.e., an access and driver TFT, one storage capacitor, and four externally accessible control lines/signals (SCAN, SUPPLY, DATA, and COMMON OLED electrode). The driving sequence is segmented functionally into four segments; (1) data sample and hold, (2) pixel illumination, (3) driver TFT compensation, and (4) OLED compensation.

[0097] It should be understood that various alternatives and modifications of the present invention. Nonetheless, the

present invention is intended to embrace all such alternatives, modifications and variances that fall within the scope of the appended claims.

What is claimed is:

- 1. A circuit for driving a current mode light modulating device, comprising:

- a capacitor for storing a data voltage;

- a field effect transistor (FET) controlled by a signal on a scan line, for coupling said data voltage from a signal line to said capacitor; and

- a current source, controlled by said stored data voltage, for driving said device with current provided from a power line,

- wherein said power line is in a plane that is geometrically parallel to a plane within which said scan line is located.

- 2. The circuit of claim 1,

- wherein said device has a terminal connected to a common electrode, and

- wherein said power line has a waveform thereon that operates in cooperation with a waveform on said common electrode to reverse bias said device to reduced trapped charge.

- 3. The circuit of claim 1,

- wherein said device has a terminal connected to a common electrode,

- wherein said power line has a first waveform thereon, said signal line has second waveform thereon and said common electrode has a third waveform thereon, and

- wherein said first, second and third waveforms cooperate with one another to reduce a threshold voltage shift of said current source.

- 4. The circuit of claim 1,

- wherein said device has a terminal connected to a common electrode,

- wherein said power line has a first waveform thereon, said signal line has second waveform thereon, said common electrode has a third waveform thereon, and said scan line has a fourth waveform thereon, and

- wherein said first, second third and fourth waveforms cooperate with one another to control said device.

- 5. The circuit of claim 1,

- wherein said FET and said current source are connected to a common node, and

- wherein said capacitor is connected between said common node and said power line.

- 6. The circuit of claim 5, wherein said capacitor employs a displacement current through bootstrapping to facilitate said storage of said data voltage.

- 7. The circuit of claim 1, wherein said power line has an alternating current (AC) waveform thereon.

- 8. The circuit of claim 1, wherein said device has a terminal connected to a common electrode with an alternating current (AC) waveform thereon.

- 9. The circuit of claim 1, wherein said device is an organic light emitting diode (OLED).

- 10. The circuit of claim 1,

- wherein said circuit is a member of a plurality of such circuits configured in a row, and

- wherein said power line and said scan line are connected to said plurality of circuits.

- 11. The circuit of claim 10.

- wherein said row is a first row in an array,

- wherein said power line is a first power line and said scan line is a first scan line,

- wherein said array includes a second row of said circuits,

- wherein said second row is connected to a second power line and a second scan line.

- 12. The circuit of claim 1, wherein said FET and said current source comprise amorphous silicon.

- 13. The circuit of claim 12, wherein said current source is biased in its saturation region.

- 14. The circuit of claim 12, wherein said current source is biased to allow current flow less than 100% of the time.

- 15. An active matrix organic light emitting diode (AMOLED) display comprising:

- a plurality of pixel circuits in a row,

- wherein each of said pixel circuits includes:

- (a) a capacitor for storing a data voltage;

- (b) a first field effect transistor (FET) controlled by a signal on a scan line, for coupling said data voltage from a signal line to said capacitor; and

- (c) a second FET, controlled by said stored data voltage, for driving an AMOLED in said display with current provided from a power line,

- wherein said power line is in a plane that is geometrically parallel to a plane within which said scan line is located, and

- wherein said power line and said scan line are connected to each of said pixel circuits in said row.

- **16**. The circuit of claim 15, wherein said first and second FET comprise amorphous silicon.

\* \* \* \* \*

| 专利名称(译)        | 有源矩阵oled电压驱动像素电路                                                                                                     |         |            |  |

|----------------|----------------------------------------------------------------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | US20030107565A1                                                                                                      | 公开(公告)日 | 2003-06-12 |  |

| 申请号            | US10/300417                                                                                                          | 申请日     | 2002-11-20 |  |

| [标]申请(专利权)人(译) | 国际商业机器公司                                                                                                             |         |            |  |

| 申请(专利权)人(译)    | 国际商业机器公司                                                                                                             |         |            |  |

| 当前申请(专利权)人(译)  | 群创光电                                                                                                                 |         |            |  |

| [标]发明人         | LIBSCH FRANK R<br>SANFORD JAMES L                                                                                    |         |            |  |

| 发明人            | LIBSCH, FRANK R.<br>SANFORD, JAMES L.                                                                                |         |            |  |

| IPC分类号         | G09G3/20 G09G3/32 G09G5/00                                                                                           |         |            |  |

| CPC分类号         | G09G3/2011 G09G3/2014 G09G3/3233 G09G2300/0426 G09G2320/043 G09G2310/0205 G09G2310 /0254 G09G2310/0256 G09G2300/0842 |         |            |  |

| 优先权            | 60/332389 2001-11-20 US                                                                                              |         |            |  |

| 其他公开文献         | US7167169                                                                                                            |         |            |  |

| 外部链接           | Espacenet USPTO                                                                                                      |         |            |  |

### 摘要(译)

提供了一种用于驱动电流模式光调制装置的电路。该电路包括(a)用于存储数据电压的电容器,(b)由扫描线上的信号控制的场效应晶体管(FET),用于将数据电压从信号线耦合到电容器,以及(c)由存储的数据电压控制的电流源,用于利用从电力线提供的电流驱动该装置。电源线位于几何平行于扫描线所在平面的平面内。